隨著電子技術的飛速發展,大容量、高速FPGA器件具有集成度高、體積小、靈活可重配置、實驗風險小等優點,在復雜數字系統中得到越來越廣泛的應用。數字電路設計采用一片FPGA器件、存儲設備和一些電氣接口匹配電路的解決方案已成為主流選擇方案。用FPGA來實現雙口RAM的功能可以很好地解決并行性和速度問題,而且其靈活的可配置特性使得基于FPGA的雙口RAM易于進行修改、測試及系統升級,可降低設計成本,縮短開發周期。

1.雙口RAM

雙口RAM是在一個SRAM存儲器上具有兩套完全獨立的數據線、地址線和讀寫控制線,并允許兩個獨立的系統同時對其進行隨機性訪問的存儲器,即共享式多端口存儲器。雙口RAM最大的特點是存儲數據共享。一個存儲器配備兩套獨立的地址、數據和控制線,允許兩個獨立的CPU或控制器同時異步地訪問存儲單元。因為數據共享。則必須具有訪問仲裁控制。內部仲裁邏輯控制提供以下功能:對同一地址單元訪問的時序控制;存儲單元數據塊的訪問權限分配:信令交換邏輯(例如中斷信號)等。雙口RAM可用于提高RAM的吞吐率,適用于實時數據緩存。

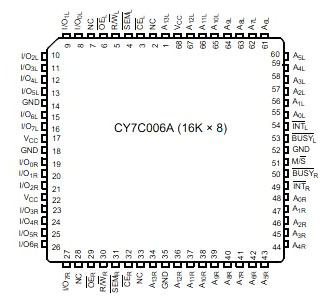

CY7C006A是Cypress公司生產的16 kb×8高速雙口靜態RAM,存取速度小于20 ns。該器件具有真正的雙端口,可以同時進行數據存取,兩個端口具有獨立的控制信號線、地址線和數據線,另外通過主/從選擇可以方便地擴存儲容量和數據寬度。通過器件的信號量標志器,左、右兩端口可以實現器件資源共享。

CY7C006A引腳圖

2.雙口RAM實現

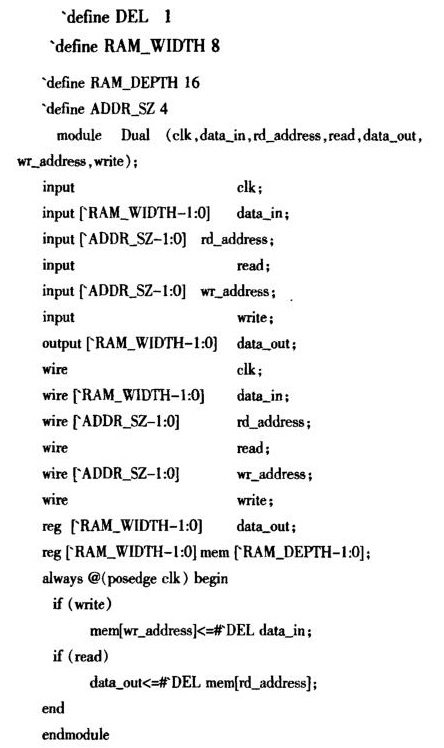

本設計采用自頂而下的設計思想。選用Xilinx公司的Spartan-6 FPGA器件,基于低功耗45 nm、9-金屬銅層、雙柵極氧化層工藝技術,提供高級功耗管理技術,150,000個邏輯單元,集成式PCI Express模塊,高級存儲器支持。250 MHz DSPslice和3.125 Gb/s低功耗收發器。通過Verilog HDL語言對雙口RAM功能的描述就能在一片FPGA器件內實現8位16字節的雙口RAM,并進行讀寫操作控制。雙口RAM讀寫操作控制Verilog HDL代碼如下:

圖1是雙口RAM的Verilog HDL代碼在Xilinx ISE中綜合后的寄存器傳輸級電路圖。

圖1 寄存器傳輸級電路

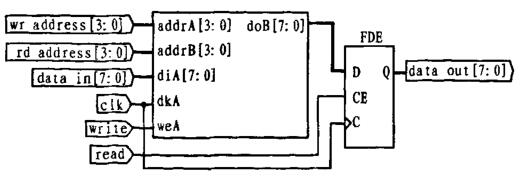

功能仿真的是Xilinx公司已經建立自己的編譯庫的Modelsim XEⅢ6.2c軟件,仿真結果如圖2所示,滿足設計要求。

圖2 雙口RAM功能仿真結果

經Xilinx ISE軟件綜合實現設計,生成可下載的比特流,將其下載到FPGA中,實現雙口RAM的功能。FPGA器件內部具有豐富的資源,可以在實現雙口RAM基本功能的基礎上。滿足系統設計的其他需求,且靈活可配置。

3.雙口RAM應用

雙口RAM在數字系統中應用廣泛。高速數據采集系統中,一般的數據傳輸系統在大數據量情況下會造成數據堵塞現象。在一些實時控制場合,實時算法經常需要由幾個DSP串行或并行工作以提高系統的運行速度和實時性。以雙口RAM構成的數據接口可以在兩個處理器之間進行高速可靠的信息傳輸。此外,雙口RAM可以應用在智能總線適配卡、網絡適配卡中作為高速數據傳輸的接口。任何一種自動控制系統都離不開數據采集系統,數據采集系統的質量直接影響整體系統的工作性能。數據采集系統高速、實時發展趨勢,對數據的傳輸和控制速度提出較高要求。而采用雙口RAM可有效提高速度,解決速度匹配問題。

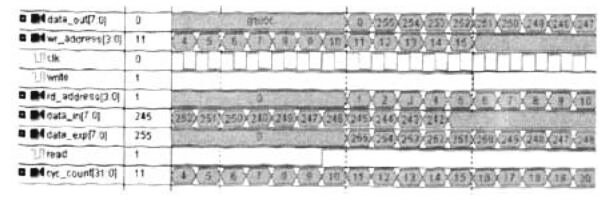

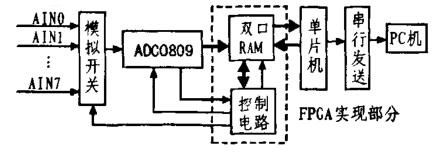

設計一塊數據采集系統板,用FPGA實現雙口RAM功能,并且控制A/D采樣與轉換,以及數據寫入雙口RAM。利用單片機控制雙口RAM的存取,構成一個獨立的數據采集系統,并可以通過串行接口把數據發送給PC機。圖3為其系統結構框圖。

圖3 數據采集系統結構框圖

首先,時鐘產生啟動信號,FPGA向采樣開關發出選通信號,選定模擬開關采樣,第0路模擬量進入,經A/D轉換后變為8位數字量并存儲于雙口RAM中,ADC0809反饋給FPGA內控制電路并告知轉換完畢,FPGA內控制電路再選通第1路模擬量進入,重復上述過程。經過0.1 ms后,時鐘又產生一個脈沖啟動信號。FPGA又重新從第O路模擬量選通。

在時鐘脈沖信號0.1 ms過程中,FPGA順序通過0~7路模擬開關,在每次選通時須判斷是否為第7路模擬量,若是則FPGA不再響應A/D反饋信號,而是等待0.1ms的時鐘脈沖信號到達再重新開始工作。單片機用于與外部PC機通信,PC機查詢是否在雙端口RAM中有新數據,并經接口電路讀人數據。其中雙口RAM具有2組獨立的數據、地址和控制總線,可對任何一個端口進行獨立的操作。若未采用雙口RAM,FPGA采取中斷方式對CPU傳輸數據時,CPU就會停止當前工作而去處理外部請求,當處理完外部事件后再回到原來被中止處,繼續原來的工作,這樣會影響CPU的速度。因此引入雙口RAM存儲FPGA傳送來的數據,然后CPU再從雙口RAM中讀數,從而提高效率。本數據采集系統采用基于FPGA雙口RAM、單片機等實現數據運行處理和控制功能,使系統的通信和處理能力大大加強,保證了系統的實時性,可以靈活地通過多種方式控制數據讀寫。

總結

以上就是基于FPGA的雙口RAM設計介紹了。本文充分利用FPGA實現了雙口RAM的基本功能,并構成了一個數據采集系統,該系統減小了設計電路的復雜性,增強了設計的靈活性和資源的可配置性。整個系統分工明確,構成合理,具有一定的應用價值。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業選用,專業的工程師幫您穩定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹